### Les Circuits Bistables (flip-flop)

- L'élément de mémoire

- La bascule RS (Reset-Set) ou SC (Set-Clear)

- La bascule JK

- La bascule D synchrone

- L'élément de mémoire D (Data)

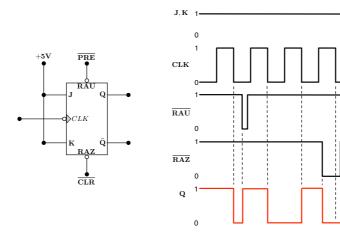

- Les entrées asynchrones (RAU/RAZ)

Basé sur: Circuits Numériques - Théorie et Applications, Ronald J. Tocci, 2° édition, Dunod Editeur, ISBN 2-10-001576-1 Bascue JK: voir l'origine du nom sur http://fr.wikipedia.org/wiki/Bascule#Origine\_du\_nom\_de\_la\_bascule\_JK

s.bolay, Electro/Info I, CFPs-EMVs, 2009

#### L'élément de mémoire (1)

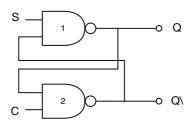

- La bascule la plus élémentaire est construite au moyen de deux portes NON-ET (NAND) ou de deux portes NON-OU (NOR ou NI).

- Les deux portes NAND sont rétro-couplées, de sorte que la sortie de la porte NAND I est connectée à l'une des entrées de la porte NAND 2 et vice-versa.

- Les sorties Q et Q\ respectivement, sont les sorties de l'élément de mémoire. Dans des conditions normales, une sortie est toujours l'inverse de l'autre.

- Les entrées de l'élément de mémoire sont désignée par:

- S (Set)

- C (Clear) ou R (Reset).

### L'élément de mémoire (2)

- Les entrées S et C se trouvent normalement toutes les deux au niveau HAUT.

- Il y a donc 2 états stables de sorties probables:

#### **NAND**

| S (ou C) | Q\ (ou Q) | Q (ou Q\) |

|----------|-----------|-----------|

| 0        | 0         | 1         |

| 0        | Ţ         | 1         |

| I        | 0         | I         |

| 1        | 1         | 0         |

L'état des sorties est fonction des niveaux <u>présents au moment de</u> l'enclenchement de la mémoire.

Pour changer l'état de sortie de la bascule, il faut momentanément en porter une au niveau BAS.

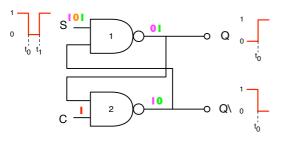

## L'élément de mémoire (3)

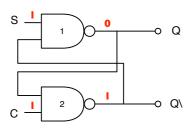

• Mise à I de l'élément de mémoire:

- Etat de départ

- Etat intérmédiaire

- Etat à l'arrivée

#### NAND

| S (ou C) | Q\ (ou Q) | Q (ou Q\) |

|----------|-----------|-----------|

| 0        | 0         | ı         |

| 0        | I         | I         |

| ı        | 0         | I         |

| ı        | I         | 0         |

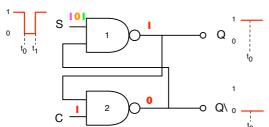

## L'élément de mémoire (4)

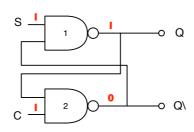

• Mise à zéro de l'élément de mémoire:

- Etat de départ

- Etat intérmédiaire

- Etat à l'arrivée

#### **NAND**

| S (ou C) | Q\ (ou Q) | Q (ou Q\) |

|----------|-----------|-----------|

| 0        | 0         | I         |

| 0        | 1         | 1         |

| ı        | 0         | I         |

| I        | 1         | 0         |

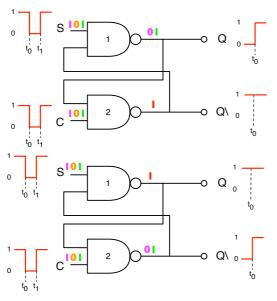

### L'élément de mémoire (5)

• Mise à zéro et à 1 simultanément de l'élément de mémoire:

- Etat de départ

- Etat intérmédiaire

- Etat à l'arrivée

#### **NAND**

| S (ou C) | Q\ (ou Q) | Q (ou Q\) |

|----------|-----------|-----------|

| 0        | 0         | 1         |

| 0        | 1         | 1         |

| Ţ        | 0         | 1         |

| I        | 1         | 0         |

Cette situation produit des niveaux HAUTS aux deux sorties simultanément, ce qui est évidemment une situation à proscrire.

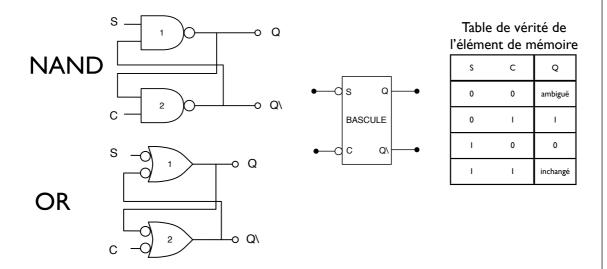

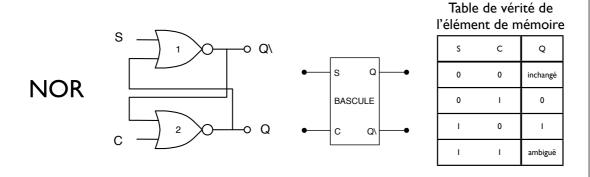

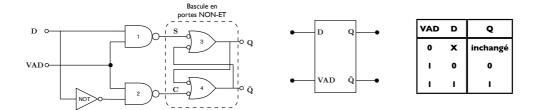

#### L'élément de mémoire (6)

• Circuits, symbole et table de vérité:

Chaque fois que nous utiliserons ce rectangle, ce sera pour représenter un élément de mémoire en NAND.

### L'élément de mémoire (7)

Circuits, symbole et table de vérité pour des éléments de mémoire en porte NOR:

L'élément de mémoire NOR fonctionne en tous points comme la mémoire NAND, à l'exception des entrées S et C qui, maintenant, sont vraies au niveau HAUT plutôt qu'au niveau BAS.

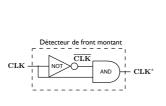

## Circuits détecteurs de fronts (1)

• Un circuit détecteur de front génère une impulsion montante étroite (CLK\*) qui se produit en coïncidence avec le front actif de l'impulsion d'horloge CLK.

- L'inverseur introduit un retard de quelques nanosecondes de sorte que le front de CLK\ a lieu légèrement plus tard que celui de CLK.

- La porte **ET** génère ainsi une pointe de tension de sortie qui est à I pendant seulement quelques nanosecondes, soit pendant le temps où CLK\ et CLK sont tous les deux au niveau **HAUT**.

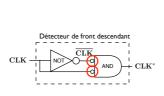

# Circuits détecteurs de fronts (\$\dagger\$)

Le montage suivant fonctionne de la même façon que pour le détecteur de front montant, mais détecte cette fois les fronts descendants.

- L'inverseur introduit un retard de quelques nanosecondes de sorte que le front de CLK\ a lieu légèrement plus tard que celui de CLK.

- La porte ET génère ainsi une pointe de tension de sortie qui est à I pendant seulement quelques nanosecondes, soit pendant le temps où CLK\ et CLK sont tous les deux au niveau BAS.

# La bascule S-C synchrone $(1)(\uparrow)$

• Symbol logique d'une bascule S-C <u>synchrone</u> déclenchée par le front <u>montant</u> du signal d'horloge:

| s | С | CLK | Q        |

|---|---|-----|----------|

| 0 | 0 | 1   | inchangé |

| 0 | ı | 1   | 0        |

| ı | 0 | 1   | ı        |

| ı | ı | 1   | ambiguë  |

- C'est donc une bascule qui passe d'un état à l'autre **seulement** lorsque le signal d'horloge effectue la transition **de 0 à 1**.

- Les entrées S et C commandent la valeur qu'on retrouve à la sortie de la bascule de la même manière que dans le cas d'un élément de <u>mémoire NI</u>, sauf qu'ici, la bascule ne modifie pas sa sortie avant qu'arrive le front montant du signal d'horloge.

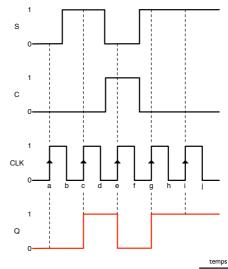

# La bascule S-C synchrone (2)(1)

• Exemple d'un signal de sortie Q en fonction des entrées S-C et du signal d'horloge (CLK):

Il est bon de noter sur cette figure que les fronts descendants <u>n'affectent</u> pas la sortie de la bascule.

Les entrées S et C ne modifient en rien la sortie de la bascule tant que le front montant du signal d'horloge n'est pas arrivé.

S et C sont les entrées de commande synchrones: ce sont elles qui dictent à la bascule l'état qu'elle devra occuper lorsque surviendra le front montant du signal d'horloge

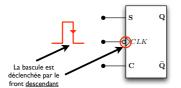

### La bascule S-C synchrone $(3)(\downarrow)$

• Symbol logique d'une bascule S-C <u>synchrone</u> déclenchée par le front <u>descendant</u> du signal d'horloge:

| s | С | CLK      | Q        |

|---|---|----------|----------|

| 0 | 0 | 1        | inchangé |

| 0 | ı | <b>+</b> | 0        |

| ı | 0 | 1        | ı        |

| ı | ı | 1        | ambiguë  |

- Le <u>petit rond</u> devant le triangle indique que la bascule réagit aux flan descendant.

- C'est donc une bascule qui passe d'un état à l'autre **seulement** lorsque le signal d'horloge CLK effectue la transition **de I à 0**.

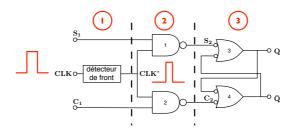

# Circuit interne d'une bascule S-C déclenchée par un signal d'horloge

- On retrouve dans un tel circuit les trois sections suivantes:

- I. Un circuit détecteur de front.

- 2. Un circuit d'aiguillage de l'impulsion constitué par les portes NON-ET 1 et 2.

- 3. Une bascule en NON-ET formée par les portes NON-ET 3 et 4.

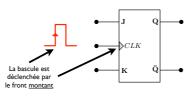

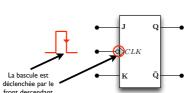

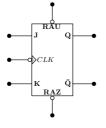

### La bascule J-K synchrone (I)

• Les entrées J et K commandent l'état de la bascule comme le font les entrées S et C de la bascule S-C synchrone, à l'exception de l'importante différence que voici:

La condition J = K = I ne donne pas lieu à une condition ambiguë!

| J | K | CLK | Q        |

|---|---|-----|----------|

| 0 | 0 | 1   | inchangé |

| 0 | ı | 1   | 0        |

| ı | 0 | 1   | ı        |

| ı | ı | 1   | bascule  |

| J | к | CLK | Q        |

|---|---|-----|----------|

| 0 | 0 | 1   | inchangé |

| 0 | ı | 1   | 0        |

| ı | 0 | 1   | ı        |

| ı | ı | 1   | bascule  |

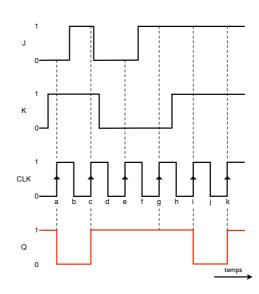

## La bascule J-K synchrone (2)

Exemple d'un signal de sortie Q en fonction des entrées J-K et du signal d'horloge (CLK):

Lorsque survient la condition J = K = I, la bascule passe toujours à l'état opposé (changement d'état) à l'arrivée du front montant du signal d'horloge (CLK). On dit que c'est le mode de basculement.

Dans ce mode, si on laisse les entrées J et K toutes les deux au niveau **HAUT**, la bascule va passer à l'état opposé à **chaque signal d'horloge**.

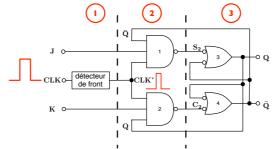

# Circuit interne d'une bascule J-K déclenchée par un signal d'horloge

- On retrouve dans un tel circuit les trois sections suivantes:

- I. Un circuit détecteur de front.

- 2. Un circuit d'aiguillage de l'impulsion constitué par les portes NON-ET 1 et 2.

- 3. Une bascule en NON-ET formée par les portes NON-ET 3 et 4.

• La seule différence par rapport au circuit interne d'une bascule S-C vient des sorties Q et Q\ qui sont ramenées sur les entrées des portes NON-ET servant à l'aiguillage de l'impulsion d'horloge.

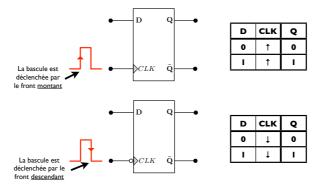

#### La bascule D synchrone (I)

• Contrairement aux bascules S-C et J-K, cette bascule ne possède qu'une entrée de commande synchrone, appelée D, pour données.

- La sortie Q prend l'état de l'entrée D à l'instant du front montant de CLK.

- Autrement dit, le niveau actuellement sur D se retrouvera mémorisé dans la bascule à l'instant du front montant.

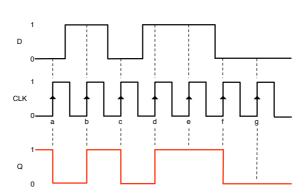

#### La bascule D synchrone (2)

Exemple d'un signal de sortie Q en fonction de l'entrée D et du signal d'horloge (CLK):

La sortie Q épouse les niveaux présents sur D à l'instant des fronts montants.

Q ne change de valeur que si un front montant survient.

L'entrée D n'a aucun effet entre deux fronts montants.

#### L'élément de mémoire D (I)

La bascule D déclenchée par un signal d'horloge possède un circuit détecteur de front qui garantit que la sortie prend la valeur de l'entrée D seulement quand se produit la transition de déclenchement du signal d'horloge. Si ce détecteur est enlevé, on obtient un circuit qui fonctionne assez différemment. Ce circuit est appelé un élément de mémoire D:

#### L'élément de mémoire D (2)

- Quand l'entrée de validation (VAD) est au niveau haut:

- la sortie Q a la même forme d'onde que D; dans ce mode, on dit que l'élément de mémoire D est <u>transparent</u>.

- Quand VAD passe au niveau BAS:

- l'entrée D est empêchée d'influencer sur l'élément de mémoire NON-ET.

- En effet, les sorties des deux portes d'aiguillage sont forcées à la valeur I.

- En d'autres mots, les sorties sont <u>verrouillées</u> sur leur niveau actuel et ne peuvent changer tant que VAD reste au niveau BAS, même si D change.

#### Les entrées asynchrones (1)

- La majeure partie des bascules **synchrones** possèdent en plus des entrées **asynchrones** qui agissent indépendamment des entrées synchrones et du signal d'horloge.

- On a recours à de telles entrées pour forcer en tout temps la remise à I ou à 0 de la bascule, quelles que soient les conditions des entrées.

- Une autre façon de présenter ces entrées est de dire que ce sont des entrées prioritaires, qui imposent un état à la bascule malgré les commandes lancées par les autres entrées.

| RAU | RAZ | Q                        |

|-----|-----|--------------------------|

| ı   | ı   | Fonctionnement synchrone |

| 0   | ı   | 1                        |

| ı   | 0   | 0                        |

| 0   | 0   | Inutilisée               |

### Les entrées asynchrones (2)

• L'exemple ci-dessous nous montre la sortie Q en fonction de RAU et RAZ en maintenant les entrées J et K à I afin de faire fonctionner le mode bascule d'une porte J-K.